數(shù)字集成電路版圖設(shè)計(jì)實(shí)踐 基于Cadence IC的簡(jiǎn)單反相器設(shè)計(jì)與太陽(yáng)能發(fā)電應(yīng)用前景

數(shù)字集成電路是現(xiàn)代電子系統(tǒng)的基石,其性能、功耗和可靠性在很大程度上由版圖設(shè)計(jì)決定。版圖設(shè)計(jì)是將電路原理圖轉(zhuǎn)化為可用于芯片制造的物理幾何圖形的過(guò)程。本文將聚焦于使用業(yè)界標(biāo)準(zhǔn)工具Cadence IC進(jìn)行一個(gè)簡(jiǎn)單反相器的版圖設(shè)計(jì),并探討其在太陽(yáng)能發(fā)電等綠色能源系統(tǒng)中的潛在應(yīng)用價(jià)值。

第一部分:Cadence IC環(huán)境下的反相器版圖設(shè)計(jì)

反相器(Inverter)是數(shù)字電路中最基本、最核心的邏輯單元,其功能是實(shí)現(xiàn)邏輯“非”運(yùn)算。一個(gè)典型的CMOS反相器由一個(gè)PMOS晶體管和一個(gè)NMOS晶體管組成。

設(shè)計(jì)流程概述:

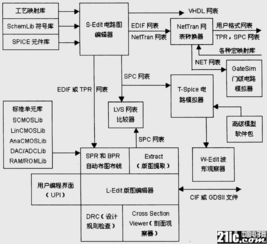

- 電路設(shè)計(jì)與仿真: 首先在Cadence Virtuoso Schematic Editor中繪制反相器的電路原理圖。設(shè)定PMOS和NMOS晶體管的尺寸(如寬長(zhǎng)比W/L),以確保正確的開(kāi)關(guān)閾值、驅(qū)動(dòng)能力和噪聲容限。完成原理圖后,使用Spectre或類似仿真工具進(jìn)行直流、瞬態(tài)和噪聲仿真,驗(yàn)證邏輯功能和性能指標(biāo)(如延遲、功耗)。

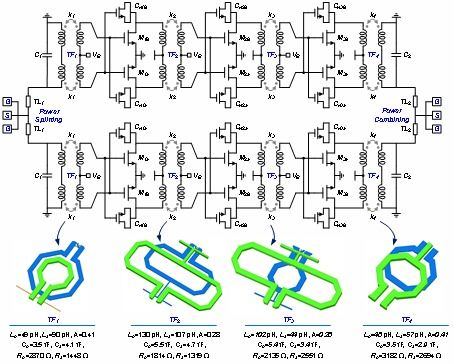

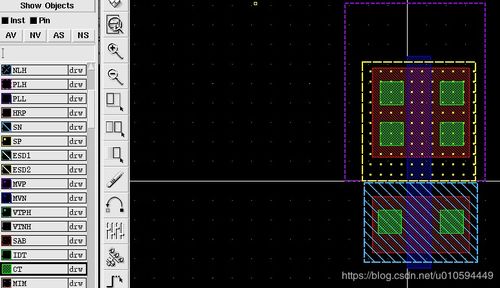

- 版圖設(shè)計(jì): 在通過(guò)電路仿真驗(yàn)證后,進(jìn)入Virtuoso Layout Editor進(jìn)行物理版圖設(shè)計(jì)。核心步驟包括:

- 創(chuàng)建單元(Cell): 為反相器創(chuàng)建一個(gè)新的版圖單元。

- 繪制有源區(qū)與晶體管: 根據(jù)設(shè)計(jì)規(guī)則(Design Rules),在相應(yīng)的層(如N-well, P-well, Active)上繪制有源區(qū),并定義PMOS和NMOS晶體管的位置。PMOS通常置于N-well中。

- 多晶硅柵極繪制: 繪制連接兩個(gè)晶體管柵極的多晶硅(Poly)條,這是反相器的輸入端。

- 源漏區(qū)接觸孔與金屬連線: 使用Contact或Via在各層之間建立電連接。用第一層金屬(Metal1)連接PMOS的源極到VDD(電源),NMOS的源極到VSS(地);將兩個(gè)晶體管的漏極用Metal1連接起來(lái),作為輸出端;將柵極多晶硅通過(guò)接觸孔連接到Metal1,作為輸入端。

- 設(shè)計(jì)規(guī)則檢查: 完成繪制后,運(yùn)行DRC(設(shè)計(jì)規(guī)則檢查),確保版圖符合晶圓廠制定的最小間距、寬度等物理規(guī)則,以保證可制造性。

- 版圖與原理圖一致性檢查: 運(yùn)行LVS(版圖與原理圖一致性檢查),確保繪制出的物理版圖與原始電路原理圖在電氣連接上完全一致。

- 寄生參數(shù)提取與后仿真: 提取版圖中的寄生電阻和電容,生成帶寄生效應(yīng)的網(wǎng)表,并進(jìn)行后仿真。這是評(píng)估實(shí)際芯片性能(如信號(hào)延遲、功耗)的關(guān)鍵步驟,通常與前仿真結(jié)果對(duì)比以評(píng)估版圖引入的影響。

設(shè)計(jì)要點(diǎn): 在版圖設(shè)計(jì)中,需要特別注意匹配性、對(duì)稱性和抗干擾能力。對(duì)于反相器,應(yīng)盡量使兩個(gè)晶體管靠近,以減少寄生效應(yīng)和工藝波動(dòng)的影響。電源線和地線應(yīng)足夠?qū)挘越档碗娮韬碗娺w移風(fēng)險(xiǎn)。

第二部分:與太陽(yáng)能發(fā)電系統(tǒng)的關(guān)聯(lián)與展望

雖然一個(gè)簡(jiǎn)單的反相器本身并不直接構(gòu)成太陽(yáng)能發(fā)電系統(tǒng),但它是構(gòu)建太陽(yáng)能發(fā)電系統(tǒng)中電力電子與控制電路不可或缺的底層單元。

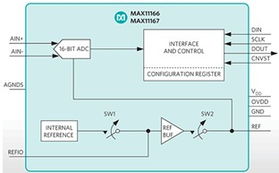

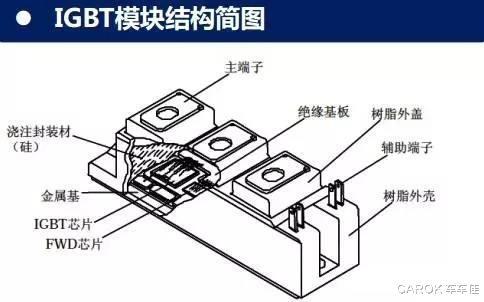

- 在太陽(yáng)能發(fā)電系統(tǒng)中的角色: 太陽(yáng)能光伏板產(chǎn)生的是直流電,而大多數(shù)家用電器和電網(wǎng)使用的是交流電。因此,需要光伏逆變器(PV Inverter)將直流電轉(zhuǎn)換為交流電。現(xiàn)代高效逆變器的核心是復(fù)雜的數(shù)字控制芯片(如DSP、MCU)和功率驅(qū)動(dòng)電路。這些芯片內(nèi)部包含了海量由反相器等基本邏輯門構(gòu)成的數(shù)字邏輯模塊,用于實(shí)現(xiàn)最大功率點(diǎn)跟蹤(MPPT)算法、脈寬調(diào)制(PWM)信號(hào)生成、系統(tǒng)狀態(tài)監(jiān)控、通信接口控制等功能。Cadence IC等工具設(shè)計(jì)的穩(wěn)定、低功耗、高可靠性的數(shù)字電路,正是這些控制芯片得以實(shí)現(xiàn)的基礎(chǔ)。

- 低功耗設(shè)計(jì)的意義: 太陽(yáng)能發(fā)電系統(tǒng)追求能量轉(zhuǎn)換和利用效率的最大化。控制芯片自身的功耗越低,系統(tǒng)的凈輸出功率就越高。通過(guò)精心的版圖設(shè)計(jì)(如優(yōu)化晶體管尺寸、布局布線以減少寄生電容),可以顯著降低數(shù)字控制電路的動(dòng)態(tài)和靜態(tài)功耗,這與太陽(yáng)能發(fā)電的綠色節(jié)能理念高度契合。

- 集成化與智能化趨勢(shì): 隨著技術(shù)發(fā)展,太陽(yáng)能發(fā)電系統(tǒng)正朝著更高集成度和更智能化的方向發(fā)展。例如,將MPPT控制器、逆變器、保護(hù)電路甚至通信模塊集成到單一芯片或封裝內(nèi)的“智能光伏模塊”已成為趨勢(shì)。這要求集成電路設(shè)計(jì),從像反相器這樣的基礎(chǔ)單元開(kāi)始,就必須具備高性能、高可靠性和高集成度的特性。Cadence IC提供的完整設(shè)計(jì)、驗(yàn)證和仿真平臺(tái),對(duì)于實(shí)現(xiàn)這類復(fù)雜的數(shù)模混合SoC(片上系統(tǒng))至關(guān)重要。

結(jié)論

從在Cadence IC中繪制一個(gè)簡(jiǎn)單反相器的版圖,到理解其在宏大的太陽(yáng)能發(fā)電產(chǎn)業(yè)鏈中的基礎(chǔ)性作用,這一過(guò)程清晰地揭示了集成電路設(shè)計(jì)從微觀到宏觀的連貫性。版圖設(shè)計(jì)不僅是幾何圖形的繪制,更是性能、功耗、可靠性和成本的綜合優(yōu)化。掌握像反相器這樣的基礎(chǔ)單元的設(shè)計(jì),是邁向更復(fù)雜數(shù)字系統(tǒng)(如太陽(yáng)能發(fā)電控制系統(tǒng)中的核心芯片)設(shè)計(jì)的第一步。隨著可再生能源的蓬勃發(fā)展,對(duì)高效、可靠的電力電子芯片需求日益增長(zhǎng),這為數(shù)字集成電路版圖設(shè)計(jì)工程師提供了廣闊的應(yīng)用舞臺(tái)和創(chuàng)新空間。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.123aa.cn/product/54.html

更新時(shí)間:2026-04-10 11:23:59